The last couple of weeks, we’ve been working on learning about FPGAs and controls. This week, we made progress on the architecture of the FPGA as well as how to communicate between different IPs. We decided on a few structural componentsu00a0 such as to place the sensor processing to motor mixing in a single IP core which communicates to a custom PWM generator. Relating to controls, we have decided to begin with a PID controller and progress onto linear quadratic or model-predictive control. For communication, we decided to use ap_none from the main IP to the PWM generator and copy the inputs on each clock cycle to preserve data integrity and allow the PWM generator to work at it’s own slower clock rate.

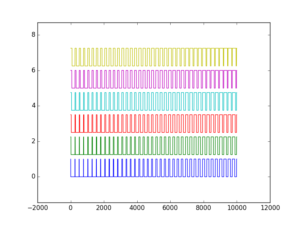

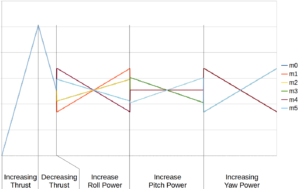

To the right are my first deliverables of the summer. I designed and tested an IP core to mix the motor commands and another one to output pwm signals to the pinouts on the PYNQ board. The top image is the motor mixer which was tested in the test benchu00a0 and plotted using LibreOffice Calc and the bottom is the output of the PWM generator and plotted using matplotlib’s pyplot.

This project is moving forward well. We are learning a lot about HLS and FPGAs. The Vivado suite is very useful for developing FPGA IPs without using Verilog or VHDL.